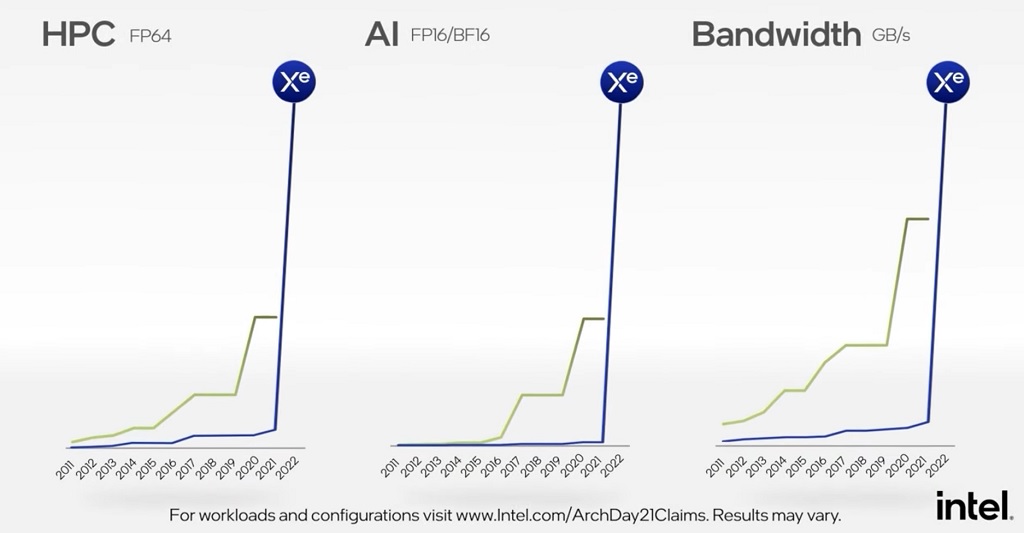

ในงาน Intel Architecture Day ที่ผ่านมา Raja M. Koduri แสดงถึงข้อมูลในงานว่าที่ผ่านมาอินเทลนั้นตามหลังอุตสาหกรรมซูเปอร์คอมพิวเตอร์ (หรือ high performance computing - HPC) ค่อนข้างมาก โดยยกตัวเลขประสิทธิภาพสามด้าน ได้แก่ ประสิทธิ์ภาพการประมวลผลเลขทศนิยม (floating point 64), ประสิทธิภาพด้านปัญญาประดิษฐ์ (bfloat16), และแบนวิดท์หน่วยความจำ ที่ชิปเฉพาะทางสามารถทำได้ดีขึ้นเรื่อยๆ ทิ้งห่างอินเทลไปไกล ทำให้ปีที่ผ่านมาอินเทลทุ่มพัฒนาชิปสำหรับตลาดซูเปอร์คอมพิวเตอร์ในชื่อ Ponte Vecchio

Ponte Vecchio เป็นหน่วยประมวลผลที่ใช้คอร์ Xe มีหน่วยประมวลผลเมทริกซ์และเวคเตอร์อย่างละ 8 ชุด พร้อมแคช หลังกจากนั้นอินเทลประกอบคอร์ Xe 16 ชุดรวมเป็น Xe Slice ที่มีหน่วยประมวลผลแบบ Ray Tracing ในตัวอีก 16 ชุด และประกอบ Xe Slice 4 ชุดเป็น Xe Stack ที่มีหน่วยเชื่อมต่อหน่วยความจำ HBM2e อีก 4 ชุด การเชื่อมต่อระหว่างชิปใช้ชิป Xe Link เชื่อมต่อ Xe Stack ได้พร้อมกัน 8 ชุด

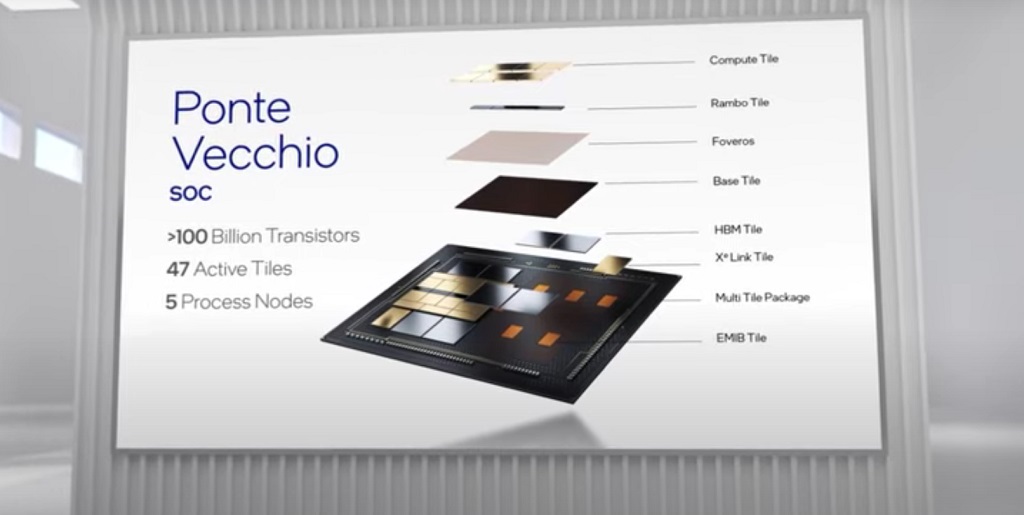

ตัวชิป Ponte Vecchio จริงๆ เป็นชิปจำนวน 47 ตัวประกอบ (เรียกว่า Tile) อยู่บนแพ็กเกจเดียวกัน โดยชิปใช้กระบวนการผลิตต่างกันถึง 5 รูปแบบ รวมทรานซิสเตอร์รวม 100 ล้านทรานซิสเตอร์ โดยชิปหลักๆ ที่อินเทลยกตัวอย่างได้แก่

- หน่วยประมวลผลหลักใช้ TSMC N5

- คอนโทรลเลอร์ที่ประกอบด้วย ตัวควบคุมหน่วยความจำ, แคช, และ PCIe Gen5 จะผลิตด้วยกระบวนการผลิต Intel 7

- Xe Link เป็นสวิตช์เชื่อมต่อระหว่าง หน่วยประมวลผล ใช้ TSMC N7

โดยรวมแล้วโมดูล Ponte Vecchio มีขนาดใหญ่มากเท่าฝ่ามือ โดยตอนนี้เป็นเพียงชิปต้นแบบ (เรียกว่า A0) พลังประมวลผลสูงกว่า 45 TFLOPS ที่ FP32 เชื่อมต่อหน่วยความจำได้แบนวิดท์มากกว่า 5TB ต่อวินาที

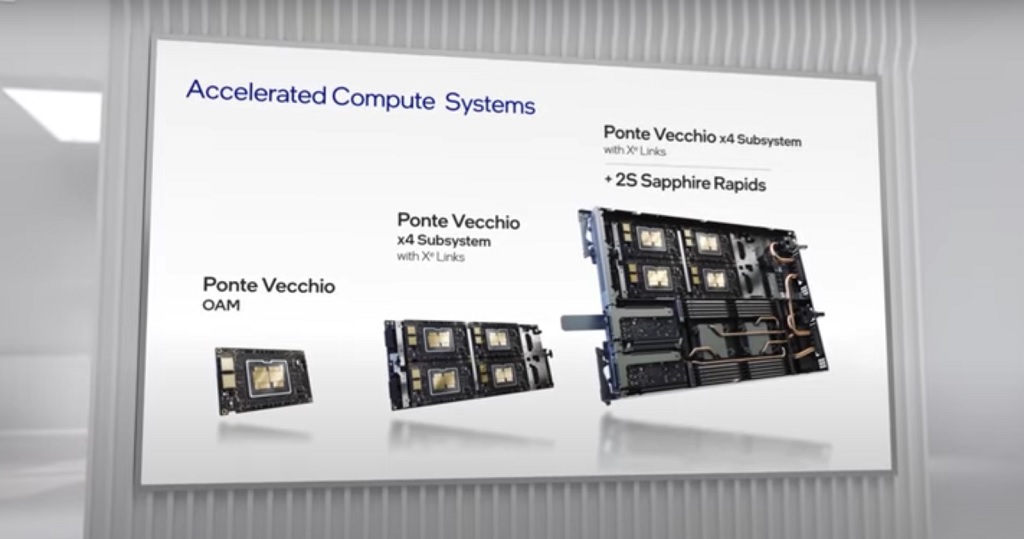

ชิป Ponte Vecchio จะขายผ่านผู้ผลิตเซิร์ฟเวอร์แบบ OEM โดยมีทั้งแบบเป็นการ์ด PCIe, โมดูลเร่งความเร็ว, และเซิร์ฟเวอร์เต็มพร้อมซีพียู Sapphire Rapids โดยยังไม่ระบุช่วงเวลาเริ่มจำหน่าย

ที่มา - Intel Architecture Day